이번에는 래치(Latch)와 플립플롭(Flip-flop1))에 대해서 알아보겠다.

회로에서 래치와 플립플롭은 1bit의 신호를 저장하기 위해 사용한다.

이게 무슨 말이냐면 어떤 신호가 회로에 공급되어 흐르다가 신호가 끊어지게 되면 그 신호를 잃게 되는데

래치와 플립플롭은 그 신호를 계속 유지한다는 것이다.

래치와 플립플롭의 차이는 클럭 신호의 유무로 구분한다. 클럭 신호를 사용하는 이유는 입력 신호의 동기화를 위한 것이다.

플립플롭은 래치의 입력에다가 클럭 신호를 논리 곱 하여, 둘 다 신호가 ON되었을 때만 동작하도록 설계한다.

결국 플립플롭을 만드려면 래치에 클럭 신호를 추가하여 입력 신호와 함께 논리 곱 게이트를 통과시키면 되는 것이니

래치와 플립플롭의 구조는 똑같다고 보면 된다. 따라서 이 글에서는 래치 혹은 플립플롭 하나씩만을 다루도록 하고

필요할 경우 클럭 신호 입력 단자를 만들거나 제거해서 플립플롭 혹은 래치로 사용하라.

이번에 다루게 될 래치는 SR 래치, T 래치, D 플립플롭, JK 래치 이다.

1. SR 래치(Set-Reset Latch, SR Latch)

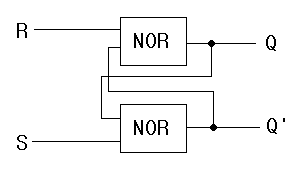

- SR 래치는 S(Set)과 R(Reset) 두 개의 입력단자를 갖고 Q와 Q'(Q의 보수)의 출력단자를 가지고 있다. 두 개의 부정 논리 합 게이트를 교차 피드백시켜서 구성한다. S에 신호가 입력되면 1, R에 신호가 입력되면 0의 출력 값(Q)을 출력하도록 한다.

위 회로를 보아 Q의 논리식은 다음과 같다.

Q = ( R + Q' )' = ( R + ( S + Q )' )' = R'ㆍ( S + Q )

S = 0, R = 0 이면

Q = 1ㆍ( 0 + Q ) = 1ㆍQ = Q, 즉 Q는 이전의 Q값을 유지한다.

S = 0, R = 1 이면

Q = 0ㆍ( 0 + Q ) = 0ㆍQ = 0, 즉 Q는 이전의 값에 상관없이 0 이 된다.

S = 1, R = 0 이면

Q = 1ㆍ( 1 + Q ) = 1ㆍ1 = 1, 즉 Q는 이전의 값에 상관없이 1 이 된다.

S = 1, R = 1 이면

Q = 0ㆍ( 1 + Q ) = 0ㆍ1 = 0, 즉 Q는 이전의 값에 상관없이 0 이 된다.

Q'의 논리식은 다음과 같다.

Q' = ( S + Q )' = ( S + ( R + Q' ) )' = S'ㆍ( R + Q' )

S = 0, R = 0 이면

Q' = 1ㆍ( 0 + Q' ) = 1ㆍQ' = Q', 즉 Q'는 이전의 Q'값을 유지한다.

S = 0, R = 1 이면

Q' = 1ㆍ( 1 + Q' ) = 1ㆍ1 = 1, 즉 Q'는 이전의 값에 상관없이 1 이 된다.

S = 1, R = 0 이면

Q' = 0ㆍ( 0 + Q' ) = 0ㆍQ' = 0, 즉 Q'는 이전의 값에 상관없이 0 이 된다.

S = 1, R = 1 이면

Q' = 0ㆍ( 1 + Q' ) = 0ㆍ1 = 0, 즉 Q'는 이전의 값에 상관없이 0 이 된다.

정리하면,

S R Q Q' State

-------------------------------

0 0 Q Q' No change

0 1 0 1 Reset

1 0 1 0 Set

1 1 0 0 Undefined

여기서 문제가 발생한다. Q와 Q'가 보수 관계에 있어야 하는데 S와 R이 모두 1인 경우에는 Q와 Q' 둘 다 0이 된다.

따라서 SR 래치는 이 정의되지 않은 입력을 가해서는 안된다는 단점이 있다.

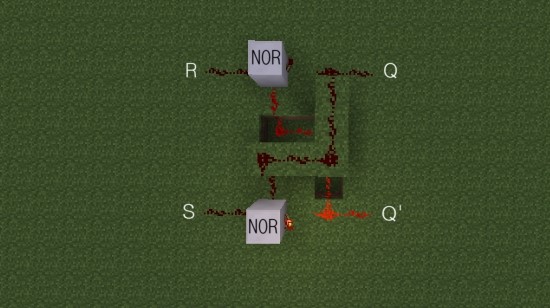

이 회로를 마인크래프트에서 똑같이 만들어 보았다.

이것이 기본적인 SR 래치의 모델이다.

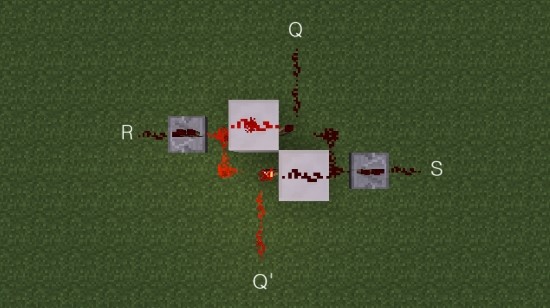

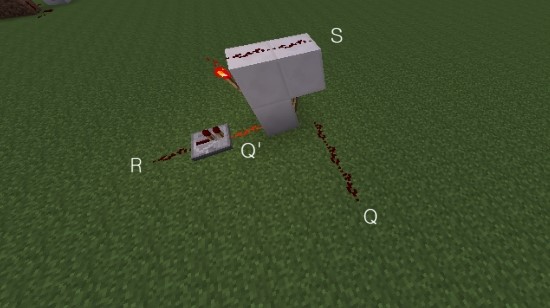

그러나 마인크래프트에서 이런 SR 래치는 잘 쓰지 않는다. 왜냐하면 축소형 모델이 존재하기 때문이다. 크기는 작으나 이 역시 훌륭한 SR 래치이기 때문에 굳이 저 회로를 만들지 않아도 된다.

축소형 모델 1

축소형 모델 2, 각도 때문에 가려졌지만 중계기가 향하는 방향에 놓인 블럭 뒤편에 레드스톤 횃불이 달려 있다. 그리고 그 레드스톤 횃불에서 나오는 신호가 바로 Q 이다.

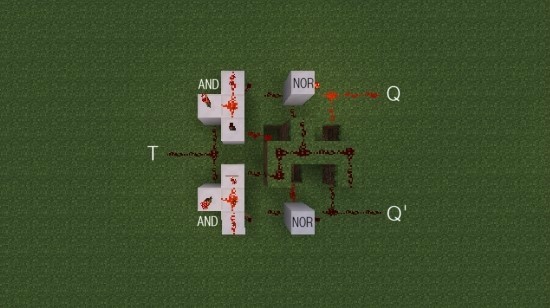

2. T 래치(Trigger Latch, T Latch)

- T 래치는 SR 래치의 확장 개념이라고 할 수 있다. T 래치는 T 신호 하나로 S와 R의 신호를 번갈아가며 입력되게 한다. 그러기 위해 두 개의 논리 곱 게이트를 추가 하였다. SR 래치의 정의되지 않은 입력 문제를 해결하기 위해 고안되었다.

위 회로를 보아 Q의 논리식은 다음과 같다.

Q = R'ㆍ( S + Q ) = ( TㆍQ )'ㆍ( TㆍQ' + Q )

T = 0 이면

Q = ( 0ㆍQ )'ㆍ( 0ㆍQ' + Q ) = 0'ㆍQ = 1ㆍQ = Q, 즉 Q는 이전의 Q값을 유지한다.

T = 1 이면

Q = ( 1ㆍQ )'ㆍ( 1ㆍQ' + Q ) = Q'ㆍ( Q' + Q ) = Q'ㆍ1 = Q', 즉 Q는 이전의 Q'값이 된다.

Q'의 논리식은 다음과 같다.

Q' = S'ㆍ( R + Q' ) = ( TㆍQ' )'ㆍ( TㆍQ + Q' )

T = 0 이면

Q' = ( 0ㆍQ' )'ㆍ( 0ㆍQ + Q' ) = 0'ㆍQ' = 1ㆍQ' = Q', 즉 Q'는 이전의 Q'값을 유지한다.

T = 1 이면

Q' = ( 1ㆍQ' )'ㆍ( 1ㆍQ + Q' ) = (Q')'ㆍ( Q + Q' ) = Qㆍ1 = Q, 즉 Q'는 이전의 Q값이 된다.

정리하면,

T Q Q' State

-------------------------

0 Q Q' No change

1 Q' Q Toggle

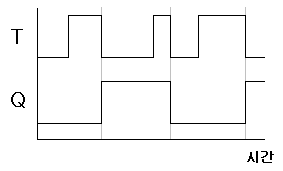

Q = 1 이면 논리 곱 게이트에 피드백 되는 신호가 위 아래 각각 1, 0 이 되고, Q' = 1 이면 각각 0, 1 이 된다. 이 때 T의 신호가 입력 되면 피드백 신호가 1인 논리 곱 게이트의 출력만 1이 되므로 S와 R에 번갈아 신호를 입력하는 결과가 된다. Q는 이전의 Q'로 Q'는 이전의 Q가 되므로 서로 교대로 ON/OFF 되는데, 이런 상태를 Toggle 이라고 부른다. T의 신호가 OFF되면 S와 R이 모두 0인 상태가 되므로 그 상태로 멈추게 될 것이다.

시간에 따른 각 입력 신호를 그래프로 그려 보았다. T가 ON 상태면 한 번은 S, 또 한 번은 R을 번갈아 가며 신호가 전달되는 것을 보기 좋게 표현한 것이다. 이렇게 하면 보는 바와 같이 S와 R이 모두 1인 경우가 발생하지 않는다. 그리고 그림에서 처럼 T의 신호를 SR 래치의 신호 주기보다 짧게 가하면 한 번은 S, 한 번은 R에 신호를 저장할 수 있다. 따라서 T의 신호를 짧게 변환시켜서 ON/OFF 순환 제어가 가능하다. 그것에 대해서는 나중에 다루도록 하겠다.

이런식으로 SR 래치에 논리 곱 게이트 두 개를 더해 연결한다. 축소형 SR 래치에 연결해도 상관 없다.

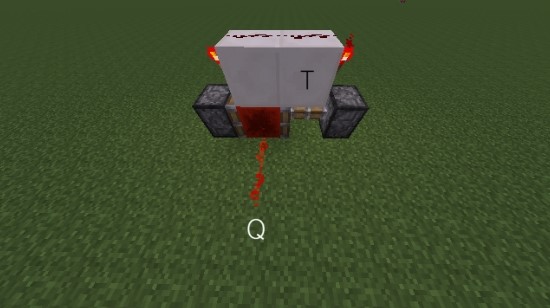

이것은 피스톤을 이용한 T 래치이다. 레드스톤 블럭이 피스톤에 의해 좌우로 밀려나는 것을 이용한 것이다. T = 1일 때 무한 발진하는 위의 회로와는 다르게 이 피스톤 T 래치는 입력 신호의 폴링 엣지(Falling Edge)2)에만 동작한다. 따라서 입력 신호 T가 길든 짧든 상관없이 한 번만 Toggle하게 된다. 일종의 버그성 작품인데 굉장히 크기가 작아 유용하게 쓰인다. 폴링 엣지의 단점은 필연적으로 회로의 응답속도3)도 느려진다는 것이다.

버튼과 같은 순간 신호를 발생시키면 신호가 OFF에서 ON이 되었다가 다시 OFF가 된다. 즉 ON 상태가 지속되는 동안 동작이 이루어지지 않고 있다가 ON에서 OFF로 다시 돌아올 때 비로소 동작하게 된다. 이것을 해결하기 위한 방법은 입력을 논리 부정 게이트를 거쳐서 파형을 뒤집어주는 방법이 있다. 그러면 입력의 라이징 엣지(Rising Edge)4)에서 T 래치가 동작한다.

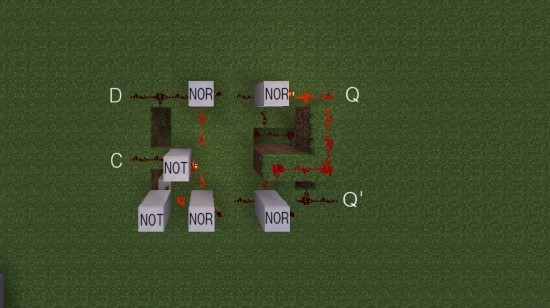

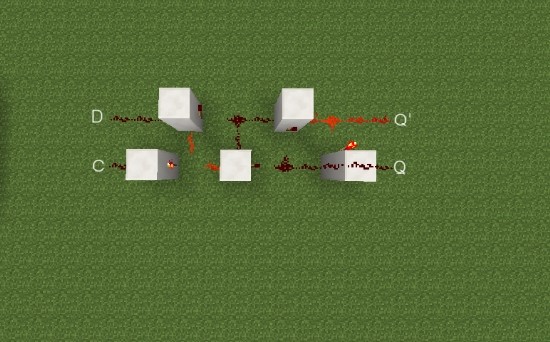

3. D 플립플롭(Data Flip-flop, D Flip-flop)

- D 플립플롭은 4개의 부정 논리 합 게이트를 사용하여 구성한다. 입력 단자 D에서 오는 신호를 클럭 신호 C가 인가될 때 Q로 출력하는 형식이다.

위 회로를 보아 Q의 논리식은 다음과 같다.

Q = R'ㆍ( S + Q ) = ( ( D + C' )' )'ㆍ( ( D' + C' )' + Q ) = ( D + C' )ㆍ( DㆍC + Q )

D = 0, C = 0 이면

Q = ( 0 + 1 )ㆍ( 0ㆍ0 + Q ) = 1ㆍQ = Q, 즉 Q는 이전의 Q값을 유지한다.

D = 0, C = 1 이면

Q = ( 0 + 0 )ㆍ( 0ㆍ1 + Q ) = 0ㆍQ = 0, 즉 Q는 이전의 값에 상관없이 0 이 된다.

D = 1, C = 0 이면

Q = ( 1 + 1 )ㆍ( 1ㆍ0 + Q ) = 1ㆍQ = Q, 즉 Q는 이전의 Q값을 유지한다.

D = 1, C = 1 이면

Q = ( 1 + 0 )ㆍ( 1ㆍ1 + Q ) = 1ㆍ1 = 1, 즉 Q는 이전의 값에 상관없이 1 이 된다.

Q'의 논리식은 다음과 같다.

Q' = S'ㆍ( R + Q' ) = ( ( D' + C' )' )'ㆍ( ( D + C' )' + Q' ) = ( D' + C' )ㆍ( D'ㆍC + Q' )

D = 0, C = 0 이면

Q = ( 1 + 1 )ㆍ( 1ㆍ0 + Q' ) = 1ㆍQ' = Q', 즉 Q'는 이전의 Q'값을 유지한다.

D = 0, C = 1 이면

Q = ( 1 + 0 )ㆍ( 1ㆍ1 + Q' ) = 1ㆍ1 = 1, 즉 Q'는 이전의 값에 상관없이 1 이 된다.

D = 1, C = 0 이면

Q = ( 0 + 1 )ㆍ( 0ㆍ0 + Q' ) = 1ㆍQ' = Q', 즉 Q'는 이전의 Q'값을 유지한다.

D = 1, C = 1 이면

Q = ( 0 + 0 )ㆍ( 0ㆍ1 + Q' ) = 0ㆍQ' = 0, 즉 Q'는 이전의 값에 상관없이 0 이 된다.

정리하면,

D C Q Q' State

-------------------------------

0 0 Q Q' No change

0 1 0 1 Reset

1 0 Q Q' No change

1 1 1 0 Set

D가 0일 때 클럭 신호 C가 1이 되면 Q가 0이 되고, D가 1일 때 클럭 신호 C가 1이 되면 Q가 1이 된다.

즉 D의 값을 그대로 Q에 저장하는 것이라고 보면 된다. 따라서 출력 Q의 신호 저장시간은 클럭 신호가 들어온 후 다음 클럭 신호가 들어오기 전까지라고 생각하면 된다. 이 성질을 이용하여 신호를 지연 및 저장시킬 수 있다. 클럭 신호 C를 계속 1상태로 지속시켜 놓으면 바로바로 D값이 Q값에 저장된다.

이론상 저렇게 구성할 수 있으나 이것 역시 축소형이 존재한다.

대표적인 평면 디자인이다.

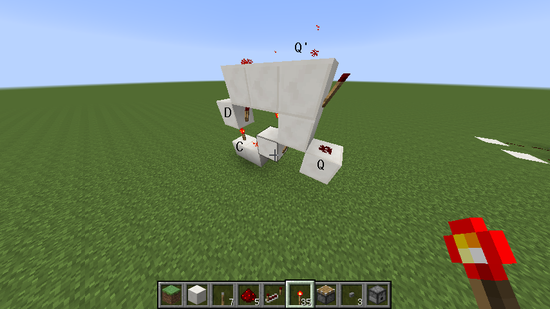

대표적인 수직 디자인이다. 커서가 가리키고 있는 블럭 오른쪽에 레드스톤 횃불이 달려 있고, 그 오른쪽 위 블럭의 왼쪽에도 달려 있다. Q'의 부분에는 레드스톤이 3개 나란히 뿌려져 있다. D라고 적힌 블럭 위에는 레드스톤이 없다.

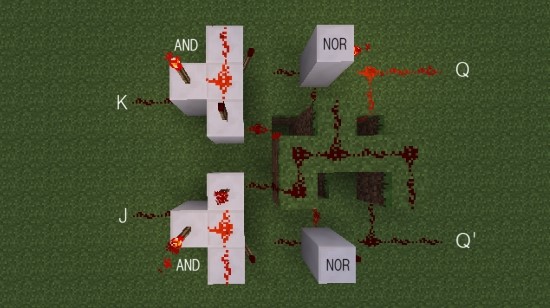

4. JK 래치(J-K Latch)

- JK 래치 역시 SR 래치의 확장 개념이라고 할 수 있다. SR 래치의 정의되지 않은 입력 문제를 해결하기 위해 고안되었다. JK 래치는 J와 K의 입력을 갖되 SR 래치와는 다르게 J = K = 1 의 상태에서도 동작이 가능하도록 설계되었다.

T 래치와 비슷하지만 입력이 J와 K로 두 가지이다. 논리식을 작성해보자,

Q = R'ㆍ( S + Q ) = ( KㆍQ )'ㆍ( JㆍQ' + Q ) = ( K' + Q' )ㆍ( JㆍQ' + Q )

J = 0, K = 0 이면,

Q = ( 1 + Q' )ㆍ( 0ㆍQ' + Q ) = 1ㆍQ = Q, 즉 이전의 Q값을 유지한다.

J = 0, K = 1 이면,

Q = ( 0 + Q' )ㆍ( 0ㆍQ' + Q ) = Q'ㆍQ = 0, 즉 이전의 값에 상관없이 Q = 0 이 된다.

J = 1, K = 0 이면,

Q = ( 1 + Q' )ㆍ( 1ㆍQ' + Q ) = 1ㆍ1 = 1, 즉 이전의 값에 상관없이 Q = 1 이 된다.

J = 1, K = 1 이면,

Q = ( 0 + Q' )ㆍ( 1ㆍQ' + Q ) = Q'ㆍ1 = Q', 즉 이전의 Q'값이 된다.

마찬가지로 Q'의 논리식은

Q' = S'ㆍ( R + Q' ) = ( JㆍQ' )'ㆍ( KㆍQ + Q' ) = ( J' + Q )ㆍ( KㆍQ + Q' )

J = 0, K = 0 이면,

Q' = ( 1 + Q )ㆍ( 0ㆍQ + Q' ) = 1ㆍQ' = Q', 즉 이전의 Q'값을 유지한다.

J = 0, K = 1 이면,

Q' = ( 1 + Q )ㆍ( 1ㆍQ + Q' ) = 1ㆍ1 = 1, 즉 이전의 값에 상관없이 Q' = 1 이 된다.

J = 1, K = 0 이면,

Q' = ( 0 + Q )ㆍ( 0ㆍQ + Q' ) = QㆍQ' = 0, 즉 이전의 값에 상관없이 Q' = 0 이 된다.

J = 1, K = 1 이면,

Q' = ( 0 + Q )ㆍ( 1ㆍQ + Q' ) = Qㆍ1 = Q, 즉 이전의 Q값이 된다.

정리하면,

J K Q Q' State

-------------------------------

0 0 Q Q' No change

0 1 0 1 Reset

1 0 1 0 Set

1 1 Q' Q Toggle

위와 같이 J = K = 1 일 때도 Q와 Q'의 값이 보수 관계이므로 정의에 위배되지 않기 때문에 이 입력값을 사용할 수 있다.

*요약

1. SR 래치 - Set과 Reset으로 1bit의 신호를 저장하는 회로

2. T 래치 - T신호로 Set과 Reset을 번갈아 반복하는 회로

3. D 플립플롭 - 클럭이 인가되는 동안 D신호를 Set하는 회로

4. JK 래치 - SR 래치와 유사하나 Set과 Reset 모두 신호가 주어졌을 때도 Toggle로써 동작하는 회로

[출처] 래치와 플립플롭(Latch & Flip-flop)|작성자 지아

출처 : http://miniskirtzia.blog.me/220054685053

'하드웨어' 카테고리의 다른 글

| Tri-state (3상 상태) 란?? (0) | 2016.08.19 |

|---|---|

| Impedance(임피던스)란? (0) | 2016.08.19 |

| Bootloader란 무엇인가? (0) | 2015.06.06 |

| Sink current, Source current (0) | 2015.05.31 |

| ROM BIOS 란? (1) | 2013.10.23 |